# Help Volume

$\ensuremath{\mathbb{C}}$  1996-2001 Agilent Technologies. All rights reserved.

Toolsets: InfiniBand (Agilent Technologies N4206A)

# Using the InfiniBand Toolset

|                                                  | The InfiniBand Toolset adds protocol-based display and error detection<br>capabilities to the logic analyzer. This toolset helps you look at<br>InfiniBand data streams traveling across 10-bit parallel data buses<br>going to, or coming from, serializer/deserializer chips. |  |  |  |  |  |  |

|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|                                                  | The InfiniBand Toolset decodes 8B/10B encoded data on the 10-bit data bus. It does not work with 10-bit parallel buses whose data has already been decoded in hardware.                                                                                                         |  |  |  |  |  |  |

|                                                  | The InfiniBand Toolset understands Data Packet and Link Packet protocols. You can modify these protocol definitions if necessary.                                                                                                                                               |  |  |  |  |  |  |

| NOTE:                                            | The InfiniBand Toolset will work with any Agilent Technologies logic analyzer whose state analysis speeds support the the speed of the 10-bit data bus.                                                                                                                         |  |  |  |  |  |  |

| "Installation and<br>Licensing" on page 8        | <ul> <li>"To check if the InfiniBand Toolset is installed" on page 8</li> <li>"To install the InfiniBand Toolset" on page 9</li> <li>"To license the InfiniBand Toolset" on page 10</li> </ul>                                                                                  |  |  |  |  |  |  |

| "Probing the Device<br>Under Test" on<br>page 12 | <ul> <li>"Step 1. Connect the logic analyzer probes" on page 12</li> <li>"Step 2. Select the state sampling mode" on page 12</li> <li>"Step 3. Label the logic analyzer channels" on page 13</li> </ul>                                                                         |  |  |  |  |  |  |

| "Capturing the Data"<br>on page 15               | <ul> <li>"To trigger on special 8B/10B codes" on page 15</li> <li>"To trigger with a second analyzer" on page 17</li> <li>"To trigger with another instrument" on page 17</li> <li>"To run the measurement" on page 19</li> </ul>                                               |  |  |  |  |  |  |

| "Displaying the Data"<br>on page 20 | • "To connect the InfiniBand Tool (in the workspace)" on page 20                                         |  |  |  |  |

|-------------------------------------|----------------------------------------------------------------------------------------------------------|--|--|--|--|

| on page 20                          | • "To set up the InfiniBand Tool" on page 21                                                             |  |  |  |  |

|                                     | • "To select the output data columns" on page 22                                                         |  |  |  |  |

|                                     | • "To filter data rows" on page 26                                                                       |  |  |  |  |

| "Modifying Protocol                 | • "To modify a protocol definition" on page 30                                                           |  |  |  |  |

| Definitions" on<br>page 30          | • "To reload the protocol definitions" on page 31                                                        |  |  |  |  |

|                                     | • "To reset the protocol definitions" on page 32                                                         |  |  |  |  |

| Reference                           | • "Protocol Definition Syntax" on page 36                                                                |  |  |  |  |

| Concepts                            | • "Passively Probing an InfiniBand System" on page 42                                                    |  |  |  |  |

|                                     | • "Basics of 8B/10B Encoding" on page 54                                                                 |  |  |  |  |

| See Also                            | Main System Help (see the <i>Agilent Technologies 16700A/B-Series Logic Analysis System</i> help volume) |  |  |  |  |

|                                     | Glossary (see page 57)                                                                                   |  |  |  |  |

Using the InfiniBand Toolset

#### Contents

#### Using the InfiniBand Toolset

#### **1** Installation Guide

Installation and Licensing 8 To check if the InfiniBand Toolset is installed 8 To install the InfiniBand Toolset 9 To license the InfiniBand Toolset 10

#### 2 Task Guide

Probing the Device Under Test 12 Step 1. Connect the logic analyzer probes 12 Step 2. Select the state sampling mode 12 Step 3. Label the logic analyzer channels 13

Capturing the Data 15 To trigger on special 8B/10B codes 15 To trigger with a second analyzer 17 To trigger with another instrument 17 To run the measurement 19

Displaying the Data 20 To connect the InfiniBand Tool (in the workspace) 20 To set up the InfiniBand Tool 21 To select the output data columns 22 To filter data rows 26

Modifying Protocol Definitions 30 To modify a protocol definition 30 To reload the protocol definitions 31 To reset the protocol definitions 32

#### Contents

#### **3 Reference**

Protocol Definition Syntax 36 Protocol Block 36 Physical Layer Definition 37 Header Block 37 Field Definition 38 Numeric Values 40

#### 4 Concepts

Passively Probing an InfiniBand System 42 InfiniBand Logic Analysis Support 42 Termination Networks 45 Logic Analyzer Connectors 51 Appendix 53

Basics of 8B/10B Encoding 54

Glossary

Index

# Installation Guide

## Installation and Licensing

The InfiniBand Toolset software may already be installed with logic analysis system software (if they are ordered at the same time).

If the InfiniBand Toolset is not already installed, you need to install it.

Once the InfiniBand Toolset is installed, you must obtain a license to use it beyond the demo period.

- "To check if the InfiniBand Toolset is installed" on page 8

- "To install the InfiniBand Toolset" on page 9

- "To license the InfiniBand Toolset" on page 10

Licensing Policy for the Logic Analysis System and Tool Sets (see the *Agilent Technologies 16700A/B-Series Logic Analysis System* help volume)

## To check if the InfiniBand Toolset is installed

- 1. In the main logic analysis system window, select the System Admin button

- 2. In the Admin tab of the System Administration Tools dialog, select the Licensing... button.

| F  | System Administration Tools                        |                                            |  |  |  |  |  |

|----|----------------------------------------------------|--------------------------------------------|--|--|--|--|--|

| Se | elect a system administration function to perform. |                                            |  |  |  |  |  |

|    | Networking                                         | Networking Admin Security Software Install |  |  |  |  |  |

| Г  |                                                    |                                            |  |  |  |  |  |

|    | About Licensing                                    |                                            |  |  |  |  |  |

3. In the Tool Sets tab of the Licensing Dialog, look for the "N4206A - InfiniBand Toolset" product.

See Also

- If it is not listed, go to "To install the InfiniBand Toolset" on page 9.

- If it is listed, go to "To license the InfiniBand Toolset" on page 10.

## To install the InfiniBand Toolset

If the CD-ROM drive is not connected to the logic analysis system, see the instructions printed on the CD-ROM package.

- 1. Turn on the CD-ROM drive first; then, turn on the logic analysis system.

- 2. Insert the CD-ROM in the drive.

- 3. In the main logic analysis system window, select the System Admin button

- 4. In the Software Install tab of the System Administration Tools dialog, select Install....

| System Administration Tools                                |         |  |  |  |

|------------------------------------------------------------|---------|--|--|--|

| Select a system administration function to pe              | erform. |  |  |  |

| Networking Admin Security Software In                      | nstall  |  |  |  |

| Install/Update or Remove a software component              |         |  |  |  |

| List the current software components, and revision<br>List |         |  |  |  |

- 5. Change the media type to "CD-ROM" if necessary, and select Apply.

- 6. Select the "AUXILIARY-SW" selection to open it.

- 7. Select the InfiniBand Toolset; then, select the Install button.

The dialog will display "Progress: completed successfully" when the installation is complete.

- 8. Select the Close button to close the Software Install window.

- 9. Select the Close button to close the System Administration Tools window.

Chapter 1: Installation Guide Installation and Licensing

10. Go to "To license the InfiniBand Toolset" on page 10.

**See Also** See the instructions printed on the CD-ROM package for a summary of the installation instructions.

#### To license the InfiniBand Toolset

- 1. To obtain a password, contact the password center listed on the Entitlement Certificate you received after purchasing the InfiniBand Toolset.

- 2. In the main logic analysis system window, select the System Admin button

- 3. In the Admin tab of the System Administration Tools dialog, select the Licensing... button.

| -               | System Administration Tools                         |  |  |  |  |  |  |

|-----------------|-----------------------------------------------------|--|--|--|--|--|--|

| Select a sys    | Select a system administration function to perform. |  |  |  |  |  |  |

| Networking      | Networking Admin Security Software Install          |  |  |  |  |  |  |

| Information     |                                                     |  |  |  |  |  |  |

| About Licensing |                                                     |  |  |  |  |  |  |

- 4. In the Tool Sets tab of the Licensing Dialog, enter the password into the field for the "N4206A InfiniBand Toolset" product.

- 5. Select OK to close the Licensing Dialog.

- 6. Select Close to close the System Administration Tools window.

- 7. Restart the session.

You are now ready to use the InfiniBand Toolset.

$\mathbf{2}$

Task Guide

# Probing the Device Under Test

To probe the device under test (also known as a target system):

- "Step 1. Connect the logic analyzer probes" on page 12

- "Step 2. Select the state sampling mode" on page 12

- "Step 3. Label the logic analyzer channels" on page 13

See Also

"Passively Probing an Infini<br/>Band System" on page  $42\,$

### Step 1. Connect the logic analyzer probes

To use the InfiniBand Toolset, you need to connect logic analyzer probe channels to:

• A 10-bit parallel data bus (going to, or coming from, an InfiniBand serializer/deserializer chip).

The InfiniBand Toolset decodes 8B/10B encoded data, so it won't work with 10-bit parallel buses whose data has already been decoded in hardware.

You also need to connect a logic analyzer CLK input channel to:

• A clock signal that identifies when the data bus is valid and should be sampled by the logic analyzer.

Next Step (see page 12)

### Step 2. Select the state sampling mode

When using the InfiniBand Toolset, the logic analyzer must be set up in the state (synchronous) sampling mode.

1. Choose the Setup... command.

2. In the Sampling tab, select the state mode.

| Sampling                                                                                                                                                           | Format   Trigger | Symbol |                       |             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------|-----------------------|-------------|

| Analyzer:                                                                                                                                                          | Analyzer <a></a> | 🔽 0n   | 2 <sub>GHz</sub> zoom | Timing Zoom |

| <ul> <li>Timing Mode - Asynchronous sampling clocked internally by analyzer</li> <li>State Mode - Synchronous sampling clocked by the Device Under Test</li> </ul> |                  |        |                       |             |

- 3. Select the state speed configuration necessary for the speed of the 10-bit data bus.

- 4. Specify the state analyzer's sampling clock input.

# Next Step (see page 13)

#### Step 3. Label the logic analyzer channels

The InfiniBand Tool requires you to set one 10-bit data label for the InfiniBand data bus channels.

# Chapter 2: Task Guide Probing the Device Under Test

To label the logic analyzer channels:

- 1. In the Format tab of the logic analyzer's setup window, insert or rename labels so that there is a 10-bit data label.

- 2. For the 10-bit data label, specify which logic analyzer pod channels are probing the data bus.

| Sampling Format Trigger Symbol |          |     |             |     |        |  |      |                 |      |

|--------------------------------|----------|-----|-------------|-----|--------|--|------|-----------------|------|

| Pod                            |          | 3   | locks<br>CC |     | Pod C2 |  |      | Pod C1          |      |

| Assignment                     | Channels |     |             |     | TTL    |  |      | TTL             |      |

| Setup/Hold                     | Hootghed | .SB | КJ          | 15  | 87     |  | ī    | 87              |      |

| 10BitData                      | [C1[9:0] | +   |             | ••• |        |  | •••• | • • * * * * * * | **** |

|                                |          |     |             |     |        |  |      |                 |      |

See Also

"Capturing the Data" on page 15

## Capturing the Data

You can set up simple triggers on 8B/10B control codes (the "K" special characters), like K27.7 for "start of Data Packet", by knowing the 10-bit encodings for these characters.

Because logic analyzer triggering resources are limited when configured for high-speed state mode sampling, it's difficult to set up more complex triggers. However, you can also:

- 1. Use the second logic analyzer or another instrument to set up a trigger on some event in the device under test.

- 2. Set up the logic analyzer that probes the 10-bit data bus to capture data when the second analyzer or other instrument's trigger occurs.

- 3. Run the measurement.

- 4. Correlate the captured data in the Listing display tool.

This section shows you how to set up triggers and run logic analyzer measurements.

- "To trigger on special 8B/10B codes" on page 15

- "To trigger with a second analyzer" on page 17

- "To trigger with another instrument" on page 17

- "To run the measurement" on page 19

### To trigger on special 8B/10B codes

Because special 8B/10B codes are assigned to things like "start of Data Packet", "start of Link Packet", etc., you can set up simple triggers by triggering on the special code values.

Remember that there are two possible codes for a "K" character, the one for positive running disparity and the one for neutral or negative running disparity, so you will have to set up to trigger on either code.

#### Chapter 2: Task Guide Capturing the Data

- 1. In the Trigger tab of the logic analyzer's setup window, select the Trigger Functions tab.

- 2. Select the "Find pattern n times" trigger function and either replace the current trigger sequence level or insert a new level.

- 3. Select the 10-bit data bus label; then, insert another occurrence of the same label.

- 4. Select "Or" between the two labels.

- 5. Enter the special code values for positive and negative parity. For example, the special code values for "start of Data Packet", K27.7, are 368 Hex and 097 Hex. The special code values for "start of Link Packet", K28.2, are 0f5 Hex and 30a Hex.

| Sampling Format Trigger Symbol                                                                                                                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Trigger FunctionsSettingsOverviewDefaultStoringStatusSave/RecallGeneral State, Telecom State, MPEG StateTrigger function libraries.                                                                                                 |

| Find pattern n times<br>Store range until pattern occurs<br>Store pattern2 until pattern1 occu<br>While storing pattern2, find patte<br>Store nothing until pattern occurs                                                          |

| Replace         Insert before         Insert after         Delete                                                                                                                                                                   |

| Trigger Sequence                                                                                                                                                                                                                    |

| Find       1       A occurrence of         8b/10b       data       =       368       Hex       0r         8b/10b       data       =       097       Hex       0r         then       Trigger and fill memory       0       0       0 |

See Also "To run the measurement" on page 19

"Displaying the Data" on page 20

#### To trigger with a second analyzer

If the second analyzer has been set up to probe other signals in the device under test and trigger on an event of interest:

- 1. In the Trigger tab of the logic analyzer's setup window, select the Trigger Functions tab.

- 2. Select the "Wait for second analyzer to trigger" trigger function and either replace the current trigger sequence level or insert a new level.

| Sampling Format Trigger Symbol                                                                                                 |                     |                    |                  |  |

|--------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------------|------------------|--|

| Trigger Functions                                                                                                              | Gettings Overview I | Default Storing St | atus Save/Recall |  |

| General State                                                                                                                  |                     | Trigger fun        | ction libraries. |  |

| Wait n external clo<br>Wait for arm in<br>Wait for second and<br>Wait for flag<br>Set/clear/pulse fla                          | Wait for 2nd ar     | alyzer             |                  |  |

| Replace                                                                                                                        | Insert before       | Insert after       | Delete           |  |

| Trigger Sequence<br>1 WAIT FOR SECOND ANALYZER TO TRIGGER<br>Wait for other machine to trigger<br>then Trigger and fill memory |                     |                    |                  |  |

"To run the measurement" on page 19

"Displaying the Data" on page 20

See Also

### To trigger with another instrument

If another instrument has been set up to probe other signals in the device under test and trigger on an event of interest:

1. In the Intermodule window, set up the logic analyzer to be armed by the

Chapter 2: Task Guide Capturing the Data

other instrument.

| -               | Intermo                           | dule  | •    |  |

|-----------------|-----------------------------------|-------|------|--|

| File Window     |                                   |       | Help |  |

|                 |                                   |       |      |  |

| Intermodule S   | (ew                               |       |      |  |

| Port In         |                                   |       |      |  |

| Port Out        | Armed by: Nothir                  | g     |      |  |

| _ Independent _ | Independent Group Run Arming Tree |       |      |  |

|                 | Group                             | Run - |      |  |

|                 |                                   |       |      |  |

|                 |                                   | É     |      |  |

|                 |                                   |       |      |  |

|                 |                                   | ć     |      |  |

| Close Help      |                                   |       |      |  |

- 2. In the Trigger tab of the logic analyzer's setup window, select the Trigger Functions tab.

- 3. Select the "Wait for arm in" trigger function and either replace the current trigger sequence level or insert a new level.

| Sampling Format Trigger                                                                                            | - Symbol    |                |              |              |

|--------------------------------------------------------------------------------------------------------------------|-------------|----------------|--------------|--------------|

| Trigger Functions Settings                                                                                         | Overview    | Default Storin | ng Status    | Save/Recal   |

| General State                                                                                                      |             | Trigger        | function     | n libraries. |

| Store n samples<br>Wait n external clock state:<br>Wait for arm in<br>Wait for second analyzer to<br>Wait for flag |             | Vvai           | t for Arm IN |              |

| Replace Insert                                                                                                     | ≥<br>before | Insert afte    | r            | Delete       |

| Trigger Sequence                                                                                                   |             |                |              |              |

| 1 WAIT FOR ARM IN<br>Wait for arm in                                                                               |             |                |              |              |

| then Trigger and fill                                                                                              | memory      |                |              |              |

See Also "To run the measurement" on page 19

"Displaying the Data" on page 20

### To run the measurement

• Select the Run button in or the Group Run button to start the measurement.

See Also "Displaying the Data" on page 20

## Displaying the Data

This section describes the options available when displaying data captured on the InfiniBand data bus.

- "To connect the InfiniBand Tool (in the workspace)" on page 20

- "To set up the InfiniBand Tool" on page 21

- "To select the output data columns" on page 22

- "To filter data rows" on page 26

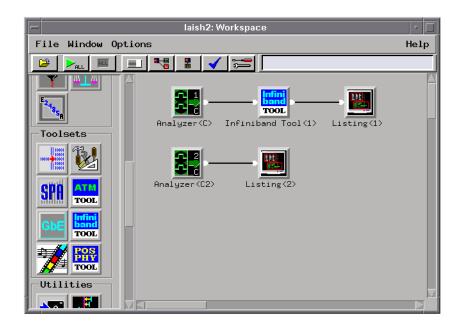

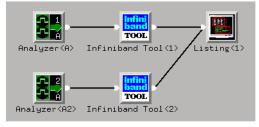

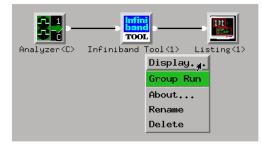

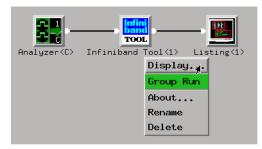

# To connect the InfiniBand Tool (in the workspace)

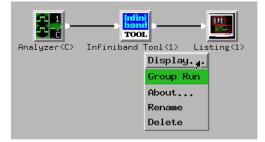

1. Drag the InfiniBand Tool icon, and drop it between the logic analyzer instrument icon and the Listing display tool icon.

The InfiniBand Tool will immediately try to decode the captured trace data. If no trace data has been captured, run a measurement.

#### **Filtering Limitation**

NOTE: When the output of two or more InfiniBand Tools go to a single Listing display, filtering does not work.

See Also "To set up the InfiniBand Tool" on page 21

"To select the output data columns" on page  $22\,$

"To filter data rows" on page 26

### To set up the InfiniBand Tool

1. Display the InfiniBand Tool.

2. In the InfiniBand Tool's Setup tab, select the appropriate options:

| 🗖 Infiniband Tool<1>                         |                        |  |  |  |  |  |

|----------------------------------------------|------------------------|--|--|--|--|--|

| File Window                                  |                        |  |  |  |  |  |

|                                              |                        |  |  |  |  |  |

|                                              |                        |  |  |  |  |  |

| Setup Filter Analysis                        |                        |  |  |  |  |  |

| Data Bus Label:                              |                        |  |  |  |  |  |

|                                              | 10BitData              |  |  |  |  |  |

| Data Packet Protocol:                        | Infiniband Data Packet |  |  |  |  |  |

| Link Packet Protocol: Infiniband Link Packet |                        |  |  |  |  |  |

| 🔲 Reverse Bits                               |                        |  |  |  |  |  |

| App1y                                        | Close                  |  |  |  |  |  |

**Data Bus Label** Selects the 10-bit parallel data bus to decode.

|   | Data Packet<br>Protocol | You should not need to modify this selection.   |

|---|-------------------------|-------------------------------------------------|

|   | Link Packet<br>Protocol | You should not need to modify this selection.   |

|   | <b>Reverse Bits</b>     | Specifies the ordering of the bits on the bus.  |

|   | 3. Select Apply to      | o change the setup.                             |

|   | 4. Select Close to      | change the setup and close the InfiniBand Tool. |

| ) | "To select the          | output data columns" on page 22                 |

|   | "To filter data         | rows" on page 26                                |

# To select the output data columns

1. Display the InfiniBand Tool.

See Also

2. In the InfiniBand Tool's Analysis tab, select the columns that should appear in the output data:

| Infiniband Tool<1>                        |  |  |

|-------------------------------------------|--|--|

| File Window                               |  |  |

|                                           |  |  |

|                                           |  |  |

| Setup Filter Analysis                     |  |  |

| Add the Following Columns to Output Data  |  |  |

| Eight Bit Data (0 for 'K' characters)     |  |  |

| ■ Character Names (ie, 'K28.8', 'D10.2')  |  |  |

| ■ BadCRC (1 when CRC is bad)              |  |  |

| ■ Bad Disparity (1 when disparity is bad) |  |  |

| Decoded Packet (Text)                     |  |  |

|                                           |  |  |

| Apply Close                               |  |  |

Eight Bit DataThe decoded bytes from the 10B codes. In the event of a<br/>special (or "K") character, the 8-bit value is set to zero<br/>because it is meaningless.Character<br/>NamesThis text column contains the character name (for<br/>example, "K28.8" or "D10.2").BadCRCThis 1-bit column contains "1" when there is an error or "0"

Chapter 2: Task Guide Displaying the Data

otherwise. The InfiniBand tool checks:

- Invariant (32-bit) CRC in Data Packets.

- Variant (16-bit) CRC in Data Packets.

- Flow Control (16-bit) CRC in Link Packets.

If a CRC code is bad, the "1" will be set on the same state as the first byte of the CRC code.

You can use this column to search for corrupt data by using the Search tab in the Listing tool. Search for BadCRD = 1.

**Bad Disparity.** This 2-bit signed integer value indicates the running disparity *at the end* of the current 10-bit value. To display this value as a signed integer, select the "Twos" (2's complement) format for the column in the Listing tool (instead of "Hex", for example).

#### Decoded

- Packet.This text column contains a description of the decoded<br/>data. Special codes (the "K" characters) and ordered sets<br/>are shown in a different color than packet headers and<br/>payloads.

- 3. Select Apply to output the selected data columns.

| <del>]</del><br>Go | ( <u> </u>   | lit Options Invasm Source                                           |          |

|--------------------|--------------|---------------------------------------------------------------------|----------|

|                    |              |                                                                     |          |

|                    |              |                                                                     |          |

| Tr                 | oto Marker   | s   Search   Comments   Analysis   Mixed Signa                      | al ]     |

| l r                | . []         |                                                                     |          |

|                    | rigger Begi  | nning End G1 G2                                                     |          |

| Got                | to State 🛓   | O L Goto                                                            |          |

| 1                  | State Number | Packet Decode                                                       | BadCRC   |

| i                  | <br>Decimal  | Text                                                                | Binary   |

|                    |              |                                                                     | 211101-3 |

|                    | 1            | Start of Data Packet (K27.7)                                        | 0        |

| 1                  | 2            | Infiniband Data Packet                                              | 0        |

|                    |              | Virtual Lane = 7 Decimal                                            |          |

|                    | -            | Link Version = 0 Decimal                                            | ~        |

|                    | 3            | Service Level = 1 Decimal<br>Reserved = 0 Decimal                   | 0        |

|                    |              | Reserved = 0 Decimal<br>Link Next Header (IBA Transport) = 1 Binary |          |

|                    |              | Link Next Header (GRH Header) = 0 Binary                            |          |

|                    | 4            | Destination Local ID = 375c Hex                                     | 0        |

|                    | 5            | Beschladion Eddal IB - 5/50 hex                                     | ŏ        |

|                    | 6            | Reserved = 00 Hex                                                   | õ        |

|                    |              | Packet Length = 14 Decimal                                          |          |

|                    | 7            |                                                                     | 0        |

|                    | 8            | Source Local ID = 17d2 Hex                                          | 0        |

|                    | 9            |                                                                     | 0        |

|                    | 10           | Base Transport Extended Header                                      | 0        |

|                    |              | Opcode = Oa Hex ((Reliable Conn) RDMA Write Only)                   |          |

|                    | 11           | Solicited Event = 0 Binary                                          | 0        |

|                    |              | MigReq = 0 Binary                                                   |          |

|                    |              | Pad Count = 2 Decimal                                               |          |

|                    | 10           | Transport Header Version = 0 Decimal                                |          |

|                    | 12<br>13     | Partition Key = 2487 Hex                                            | 0        |

|                    | 13<br>14     | Reserved = 00 Hex                                                   | 0<br>0   |

|                    | 15           | Destination QP = 87b1b3 Hex                                         | 0        |

|                    | 16           |                                                                     | 0        |

|                    | 17           |                                                                     | ŏ        |

|                    | 18           | Acknowledge Request = 0 Binary (Acknowledge Not F                   |          |

|                    |              | Reserved = 00 Hex                                                   |          |

|                    | 19           | Packet Sequence Number = Odec2a Hex                                 | 0        |

|                    | 20           |                                                                     | 0        |

|                    | 21           |                                                                     | 0        |

|                    | 22           | Payload (Infiniband Data Packet)                                    | 0        |

|                    | 23           | Payload (Infiniband Data Packet)                                    | 0        |

4. Select Close to output the selected columns and close the InfiniBand Tool.

"To set up the InfiniBand Tool" on page 21

"To filter data rows" on page  $26\,$

See Also

Chapter 2: Task Guide **Displaying the Data**

## To filter data rows

1. Display the InfiniBand Tool.

2. In the InfiniBand Tool's Filter tab, select the type of states that should be output as rows of data:

|                                               | Infiniband Tool<1> |  |  |

|-----------------------------------------------|--------------------|--|--|

| File Window                                   |                    |  |  |

|                                               |                    |  |  |

| Setup Filter Analysis<br>Show States of Type: |                    |  |  |

| ⊒ Idle                                        | Color              |  |  |

| Control Symbols                               | Color              |  |  |

| Packet Headers                                | Color              |  |  |

| ■ Packet Payloads                             | Color              |  |  |

| 🗏 Blank Lines                                 |                    |  |  |

| 🔳 Unknown States                              | Color              |  |  |

| Apply                                         | Close              |  |  |

- Idle.

- Control Symbols.

- Packet Headers.

- Packet Payloads.

- Blank Lines.

- Unknown States.

To change the color of a state type, select the Color... button.

3. Select Apply to output the selected data rows.

|                                        | Listing<1>                                       |        |            |

|----------------------------------------|--------------------------------------------------|--------|------------|

| File Window Edit Options Invasm Source |                                                  |        |            |

|                                        |                                                  |        |            |

|                                        |                                                  |        |            |

| Goto Markers Search C                  | comments   Analysis   Mixed Signa                | 1      |            |

| Trigger Beginning End G                | 1 62                                             |        | _          |

| Trigger Beginning End G                |                                                  |        |            |

| Goto State 🛓 🙆 🕴                       | Goto                                             |        |            |

|                                        |                                                  |        | _          |

| State Number Packet Decode             | 1                                                | BadCRC | Di         |

| Decimal Text                           |                                                  | Binary | Τω         |

|                                        |                                                  | Dinarg |            |

| 1 Start of Data P                      | acket (K27.7)                                    | 0      | +1         |

| 2 Infiniband Data                      | Packet                                           | 0      | +1         |

| Virtual Lane =                         | 7 Decimal                                        |        |            |

| Link Version =                         |                                                  |        |            |

| 3 Service Level =                      |                                                  | 0      | +1         |

| Reserved = 0 De                        |                                                  |        |            |

|                                        | r (IBA Transport) = 1 Binary                     |        |            |

|                                        | r (GRH Header) = 0 Binary                        |        |            |

|                                        | al ID = 375c Hex                                 | 0      | +1         |

| 6 Reserved = 00 H                      |                                                  | 0      | -1         |

| Packet Length =                        |                                                  |        |            |

| 8 Source Local ID                      |                                                  | 0      | +1         |

|                                        | t Extended Header                                | 0      | +1         |

| Upcode = Va H<br>11 Solicited Eve      | ex ((Reliable Conn) RDMA Write Only)             | 0      | +1         |

| MigReq = 0 Bi                          |                                                  | Ų      | +1         |

| Pad Count = 2                          |                                                  |        |            |

|                                        | der Version = O Decimal                          |        |            |

| 12 Partition Key                       |                                                  | 0      | +1         |

| 14 Reserved = 00                       |                                                  | ŏ      | +1         |

|                                        | P = 87b1b3 Hex                                   | Ó      | +1         |

| 18 Acknowledge R                       | equest = 0 Binary (Acknowledge Not F             | 0      | +1         |

| Reserved = 00                          | Hex                                              |        |            |

| 19 Packet Sequen                       | ce Number = Odec2a Hex                           | 0      | +1         |

| 22 Payload (I                          | nfiniband Data Packet)                           | 0      | -1         |

|                                        | nfiniband Data Packet)                           | 0      | -1         |

|                                        | nfiniband Data Packet)                           | 0      | +1         |

|                                        | nfiniband Data Packet)                           | 0      | +1         |

|                                        | nfiniband Data Packet)                           | 0      | -1         |

|                                        | nfiniband Data Packet)                           | 0      | +1         |

|                                        | nfiniband Data Packet)<br>-Sizibard Data Packet) | 0      | -1         |

|                                        | nfiniband Data Packet)<br>                       | 0<br>0 | -1<br>+1   |

|                                        | nfiniband Data Packet)<br>nfiniband Data Packet) | 0      | +1<br>+1   |

| Fayload (I                             | nrinipanu Data Facket/                           | 0      | <b>T</b> I |

|                                        |                                                  |        |            |

|                                        |                                                  |        |            |

4. Select Close to close the InfiniBand Tool.

See Also

Filtering Limitation in "To connect the InfiniBand Tool (in the work space)" on page  $20\,$

"To set up the InfiniBand Tool" on page 21

"To select the output data columns" on page  $22\,$

## Modifying Protocol Definitions

This section shows you how to modify the protocol definitions used with the InfiniBand Toolset.

- "To modify a protocol definition" on page 30

- "To reload the protocol definitions" on page 31

- "To reset the protocol definitions" on page 32

### To modify a protocol definition

1. In the InfiniBand Tool's Setup tab, select either the data packet protocol button or the link packet protocol button.

| Infiniband Tool<1>    |                        |  |

|-----------------------|------------------------|--|

| File Window           |                        |  |

|                       |                        |  |

| Setup Filter Analysis |                        |  |

| Data Bus Label:       |                        |  |

|                       | 10BitData              |  |

| Data Packet Protocol: | Infiniband Data Packet |  |

| Link Packet Protocol: | Infiniband Link Packet |  |

| ☐ Reverse Bits        |                        |  |

| Apply                 | Close                  |  |

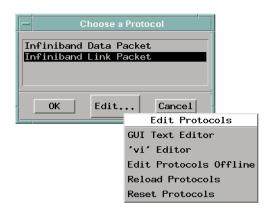

2. In the Choose a Protocol dialog, select the Edit... button, and choose either GUI Text Editor, 'vi' Editor, or Edit Protocols Offline.

3. When you are done editing protocol definitions, choose the Reload Protocols command to tell the InfiniBand Tool that changes have been made (see "To reload the protocol definitions" on page 31).

| About the Protocol<br>Definitions File | The protocol definitions file is:<br>/logic/auxiliary/TeleCom/protocols/infiniband.pro                                                                                                                                                                             |  |  |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                        |                                                                                                                                                                                                                                                                    |  |  |

|                                        | When the logic analysis system's file system is mounted by (or made<br>available to) another computer on the network, you can use any ASCII<br>text editor to modify the protocol definitions file. Don't forget to use<br>the Reload Protocols command afterward. |  |  |

| See Also                               | "Protocol Definition Syntax" on page 36                                                                                                                                                                                                                            |  |  |

## To reload the protocol definitions

After the protocol definitions file has been edited with "vi" (or some other ASCII text editor on a networked computer), you must use the Reload Protocols command to tell the InfiniBand Toolset that changes have been made.

1. In the InfiniBand Tool's Setup tab, select either the data packet protocol button or the link packet protocol button.

| Infiniband Tool<1>    |                        |  |  |

|-----------------------|------------------------|--|--|

| File Window           |                        |  |  |

|                       |                        |  |  |

|                       |                        |  |  |

| Setup Filter Analysis |                        |  |  |

| Data Bus Label:       |                        |  |  |

|                       | 10BitData              |  |  |

| Data Packet Protocol: | Infiniband Data Packet |  |  |

| Link Packet Protocol: | Infiniband Link Packet |  |  |

| □ Reverse Bits        |                        |  |  |

| Apply                 | Close                  |  |  |

2. In the Choose a Protocol dialog, select the Edit... button, and choose Reload Protocols.

| 🗕 Choose a                             | Protocol               |

|----------------------------------------|------------------------|

| Infiniband Data P<br>Infiniband Link P |                        |

| OK Edit.                               | Cancel                 |

|                                        | Edit Protocols         |

|                                        | GUI Text Editor        |

|                                        | 'vi' Editor            |

|                                        | Edit Protocols Offline |

|                                        | Reload Protocols       |

|                                        | Reset Protocols        |

## To reset the protocol definitions

If you want to return to the factory default protocol definitions, you can use the Reset Protocols command.

**CAUTION:** Resetting the protocol definitions will delete any new or modified protocol definitions.

1. In the InfiniBand Tool's Setup tab, select either the data packet protocol button or the link packet protocol button.

| Infiniband Tool<1>    |                        |  |

|-----------------------|------------------------|--|

| File Window           |                        |  |

|                       |                        |  |

|                       |                        |  |

| Setup Filter Analysis |                        |  |

| Data Bus Label:       |                        |  |

|                       | 10BitData              |  |

| Data Packet Protocol: | Infiniband Data Packet |  |

| Link Packet Protocol: | Infiniband Link Packet |  |

| ☐ Reverse Bits        |                        |  |

| Apply                 | Close                  |  |

2. In the Choose a Protocol dialog, select the Edit... button, and choose Reset Protocols.

| - Choose a                                       | Protocol                   |  |

|--------------------------------------------------|----------------------------|--|

| Infiniband Data Packet<br>Infiniband Link Packet |                            |  |

| OK Edit.                                         | Cancel -<br>Edit Protocols |  |

|                                                  | GUI Text Editor            |  |

|                                                  | 'vi' Editor                |  |

|                                                  | Edit Protocols Offline     |  |

|                                                  | Reload Protocols           |  |

|                                                  | Reset Protocols            |  |

Chapter 2: Task Guide Modifying Protocol Definitions

# Reference

This section describes the protocol definition syntax.

Protocol definitions are used by the InfiniBand Tool to decode captured data.

- "Protocol Block" on page 36

- "Physical Layer Definition" on page 37

- "Header Block" on page 37

- "Field Definition" on page 38

- "Data" on page 38

- "Symbols" on page 38

- "ProtocolIndicator" on page 39

- "Numeric Values" on page 40

#### Example

Here is the definition for the Infiniband Link Packet protocol:

```

Protocol

{

Name "Infiniband Link Packet"

PhysicalLayer 1

Header

{

OP "Operand" 4 Hex Symbols

{

"IBA Flow Control (Normal)" #h0

"IBA Flow Control (Init)" #h1

}

FCTBS "Flow Control Total Blocks Sent" 12 Decimal Data

VL "Virtual Lane" 4 Decimal Data

FCCL "Flow Control Credit Limit" 12 Decimal Data

}

}

```

See Also

"Displaying the Data" on page 20

#### **Protocol Block**

```

Syntax

```

Protocol ∫

Name "protocol name"

|          | }<br>A protocol definition starts with the keyword "Protocol"; then, the<br>definition is enclosed in brackets "{ }". |

|----------|-----------------------------------------------------------------------------------------------------------------------|

|          | The first line inside defines the name of the protocol (which must be enclosed in double quotes).                     |

| Example  | Protocol<br>{<br>Name "Infiniband Link Packet"<br>}                                                                   |

| See Also | "Physical Layer Definition" on page 37<br>"Header Block" on page 37                                                   |

# Physical Layer Definition

Syntax

PhysicalLayer 1

After the Name definition in a Protocol block is an optional physical layer definiton.

The "PhysicalLayer" definition is only required if the protocol can be used as a MAC layer or Physical layer. In other words, it is used for protocols that are at the bottom of the protocol stack on an InfiniBand data bus.

Example

PhysicalLayer 1

Header Block

After the Protocol block and possibly a physical layer definition is the list of fields in the header, enclosed in the "Header {}" block.

| Example  | Header<br>{<br>field definitions<br>} |

|----------|---------------------------------------|

| See Also | "Field Definition" on page 38         |

|          | Field Definition                                                                                                                                                                                                                                                                               |  |  |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax   | 'Mnemonic' "'Full Name'" 'Width(in bits)' 'Format' 'Type'<br>For each field defined in a Header block, there is a line with a short 2-<br>or 3-letter Mnemonic, a full name (enclosed in double-quotes), the<br>length of the field (in bits), a format specification, and a type indicator.   |  |  |

|          | The choices for field format are:                                                                                                                                                                                                                                                              |  |  |

|          | • Binary                                                                                                                                                                                                                                                                                       |  |  |

|          | • Octal                                                                                                                                                                                                                                                                                        |  |  |

|          | • Hex                                                                                                                                                                                                                                                                                          |  |  |

|          | • Decimal                                                                                                                                                                                                                                                                                      |  |  |

|          | The choices for field type are:                                                                                                                                                                                                                                                                |  |  |

|          | • "Data" on page 38                                                                                                                                                                                                                                                                            |  |  |

|          | • "Symbols" on page 38                                                                                                                                                                                                                                                                         |  |  |

|          | • "ProtocolIndicator" on page 39                                                                                                                                                                                                                                                               |  |  |

| Example  | VL "Virtual Lane" 4 Decimal Data<br>This is the third field in the Infiniband Link Packet header, the Virtual<br>Lane. It is 4 bits long. It should be displayed as a Decimal value, and it's<br>a "Data" field.                                                                               |  |  |

|          | Data                                                                                                                                                                                                                                                                                           |  |  |

|          | Data says to display the numeric value of the field in the format specified.                                                                                                                                                                                                                   |  |  |

| See Also | "Field Definition" on page 38                                                                                                                                                                                                                                                                  |  |  |

|          | Symbols                                                                                                                                                                                                                                                                                        |  |  |

|          | The Symbols field type says there is a table of text names for various values in the field. If a value matches one of these, the decoder will display the name of the value, instead of the numeric value. Otherwise, the field will be displayed as a numeric value, in the format specified. |  |  |

| Example  | Here is the "Precedence" field from an IP (Internet Protocol)<br>definition:                                                                                                               |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | <pre>PR "Precedence" 3 Hex Symbols {     "Routine" 0     "Priority" 1     "Immediate" 2     "Flash" 3     "Flash Override" 4     "Internetwork Control" 6     "Network Control" 7 }</pre>  |

|          | Notice that the "Symbols" field type is followed by a symbol table description, enclosed in "{ }" brackets. For each symbol, there is a name (in double-quotes) and a numeric value.       |

| See Also | "Field Definition" on page 38                                                                                                                                                              |

|          | "Numeric Values" on page 40                                                                                                                                                                |

|          | ProtocolIndicator                                                                                                                                                                          |

|          | The ProtocolIndicator field type is how a protocol references the next layer of the protocol stack.                                                                                        |

|          | The syntax for this type is exactly the same as for "Symbols" on page 38, except that each symbol's name is the name of another protocol, which must also be defined in the protocol file. |

| Example  | Here is the "Length/Type" field of the Ethernet protocol:                                                                                                                                  |

|          | PT "Length/Type" 16 Hex ProtocolIndicator                                                                                                                                                  |

|          | <pre>{   "Internet Protocol" #h0800   "ARP Request" #h0806   "ARP Response" #h0835   "AppleTalk Datagram Protocol" #h809B   "Novell IPX" #h8137   "IPS" #h2007 }</pre>                     |

|          | A value of 0x0800 in the length/type field indicates Internet Protocol,                                                                                                                    |

|          | which must also be defined in the protocol definitions file.                                                                                                                               |

| NOTE:    | While many protocols are already defined, not all possible values and protocols have been included in the protocol definition.                                                             |

| See Also | "Field Definition" on page 38                                                                                                                                                              |

Chapter 3: Reference Protocol Definition Syntax

"Symbols" on page 38

"Numeric Values" on page 40

# Numeric Values

Numeric values can be plain decimal numbers, or they can be hex, octal, or binary numbers in the following formats:

For Hex, a number is specified like this: #hff00 For Binary, like this: #b111111100000000 For Octal, like this: #q177400

The reason for these somewhat unusual formats is because the letter 'X' often means "Don't Care" in the logic analysis system, so 0xff could be misinterpreted as a value with a don't care digit. And, the 'q' in the Octal specifier is to avoid the similarity between the letter 'o' and the number '0'.

# Concepts

| Passively Probing an | InfiniBand System |

|----------------------|-------------------|

|----------------------|-------------------|

This application note describes the techniques required for passively probing a parallel InfiniBand channel with an Agilent Technologies 16700-series logic analysis system.

| "InfiniBand Logic               | • "Terminology" on page 43                                     |

|---------------------------------|----------------------------------------------------------------|

| Analysis Support" on<br>page 42 | • "Generic Block Diagram" on page 43                           |

|                                 | • "Agilent Technologies HDMP-2634 SERDES ASICs" on page 44     |

|                                 | • "Logic Analysis Features" on page 44                         |

| "Termination                    | • "Built-in Termination Networks" on page 46                   |

| Networks" on page 45            | • "Discrete Termination Networks" on page 46                   |

|                                 | • "Routing Techniques" on page 49                              |

| "Logic Analyzer                 | • "Mictor Connectors" on page 51                               |

| Connectors" on<br>page 51       | • "Connector Placement Techniques" on page 51                  |

|                                 | • "Mictor Connector Pinout" on page 52                         |

| "Appendix" on                   | • "Supported Logic Analyzer Modules for InfiniBand" on page 53 |

| page 53                         | • "Probing Part Numbers and Ordering Information" on page 53   |

|                                 | • "Supplemental Agilent Documentation" on page 53              |

|                                 | • "Technical Support" on page 53                               |

## InfiniBand Logic Analysis Support

- "Terminology" on page 43

- "Generic Block Diagram" on page 43

- "Agilent Technologies HDMP-2634 SERDES ASICs" on page 44

• "Logic Analysis Features" on page 44

## Terminology

| SerDes | Serializer / De-serializer ASIC (typically pronounced: Sir-Deez).                   |

|--------|-------------------------------------------------------------------------------------|

| IBA    | InfiniBand Architecture.                                                            |

| SUT    | Signal Under Test.                                                                  |

| SMT    | Surface Mount.                                                                      |

| РСВ    | Printed Circuit Board.                                                              |

| LVTTL  | Low Voltage TTL Logic.                                                              |

| SSTL-2 | Stub Series Terminated Logic (2.5 Volt).                                            |

| Mictor | Amp Matched Impedance Connector (used with high-<br>density logic analyzer cables). |

| 8B/10B | InfiniBand data coding scheme.                                                      |

## **Generic Block Diagram**

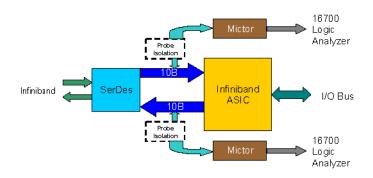

Due to loading restrictions and logic analyzer performance, probing raw differential InfiniBand data with a logic analyzer is nearly impossible. The logic analyzer must probe the de-serialized data to passively measure traffic on Infiniband channels. For systems utilizing discrete SerDes chips, the parallel data is available to route to logic analyzer connectors. Mictor connectors, along with optional isolation circuitry to minimize logic analyzer loading on the parallel data, are connected to the 10-bit bus running between the SerDes and the Infiniband controller ASIC. A simplified block diagram of this connection scheme is shown:

# Chapter 4: Concepts Passively Probing an InfiniBand System

Systems which contain the SerDes built into a custom ASIC will require an auxiliary bus to output the parallel data to the ASIC pins to be compatible with a logic analyzer. Without an external SerDes or auxiliary bus the 8B/10B traffic is not observable and cannot be probed by the logic analyzer.

## Agilent Technologies HDMP-2634 SERDES ASICs

This app note supports probing and analysis of the Agilent Technologies HDMP-2634 SerDes.

The Agilent SerDes drives 8B/10B encoded data at 10-bits x 125 MHz (DDR) at an SSTL-2 logic level. The data is sampled by the logic analyzer on both the rising and falling edge of the clock for an effective data rate of 250 MHz. Data is displayed on the logic analyzer in raw 8B/10B encoded format, unless the InfiniBand Toolset is used to convert and decode the data.

## **Logic Analysis Features**

When Mictor connectors are designed into into your InfiniBand HCA and TCA systems, you can use the 16700-series logic analysis system for full real-time acquisition of InfiniBand traffic along with concurrent transactions on other system buses such as PCI-X, CPU buses, PC266 DDR, and Rambus. Events on one bus can trigger measurements on all buses, and the events captured on each bus can be displayed in timecorrelated views.

Triggering

When capturing 8B/10B Infiniband traffic, the logic analyzer will be

|                      | capturing data at 250 MHz. At this speed, the logic analyzer must be set to the 400 MHz state sampling mode (or the 333 MHz state sampling mode for the 16717), in which the number of available sequence levels is 6. |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Generic Data Display | The logic analyzer contains a waveform viewer, and linear listing<br>window to view sampled data. Both of these tools display the data in<br>the raw format that was sampled by the logic analyzer.                    |

| InfiniBand Toolset   | You can use the InfiniBand Toolset in the 16700-series logic analysis system to display decoded 8B/10B data and detect errors in the data stream.                                                                      |

# **Termination Networks**

Termination networks are required for probing a digital signal. The termination network isolates the logic analyzer cabling and sensing circuitry from the signal under test and provides a high impedance, low capacitance load at the probe point.

Additional information about probing with Agilent Technologies logic analyzers can be found at www.agilent.com.

- "Built-in Termination Networks" on page 46

- "Discrete Termination Networks" on page 46

- "Designing a Discrete RCR Termination Network" on page 47

- "Equivalent Load" on page 48

- "Extrapolating T1 and T2 Trace Lengths" on page 49

- "Routing Techniques" on page 49

- "Series Terminated LVTTL" on page 49

- "Load Terminated LVTTL" on page 50

- "SSTL-2" on page 50

- "SSTL-3" on page 50

Chapter 4: Concepts

Passively Probing an InfiniBand System

## **Built-in Termination Networks**

The first and simplest technique for probing the output of the SerDes ASIC is to use cabling from Agilent Technologies with the termination networks built into the cable tip (E5346A high-density cable).

Signals are simply routed on the printed-circuit board to Mictor connectors and terminated internally on the connection cable. Connector placement is critical to minimize the stub length to minimize reflections on signals with fast rise times. However, even the best routing cannot eliminate the stubs completely since the path to the connector and the cable tip is a stub.

The general rule of thumb is to keep the stub length less than 1/5 the rise time of the signal under test (SUT). Refer to the following equations for deciding whether to use built in termination networks.

```

lstub <= 1/5 * risetime / propspeed

lstub <= 1/5 * risetime / propspeed <= 1/5 * 1000ps / (150ps / in) <= 1.3 in.

(lns risetime)

lstub <= 1/5 * risetime / propspeed <= 1/5 * 500ps / (150ps / in) <= 0.65 in.

(500ps risetime)</pre>

```

Whenever it is possible to route the signals within the previous constraints, use the built in termination networks. They are designed for the Agilent Technologies logic analysis systems and are compensated to provide flat frequency response between the signal under test and the logic analyzer input comparators.

The Agilent SerDes has a roughly 1-1.5 ns rise time, which require traces to be kept in between 1.3 - 2 inches in length.

## **Discrete Termination Networks**

When routing constraints prohibit using the built-in termination networks, external components can be designed into the circuit to increase the length between the logic analyzer connector and the signal under test. However, this is only recommended under rare cases when routing issues prohibit the use of standard cabling. Discrete termination networks are complex to design and are beyond the scope of this document to treat in the general case. Two solutions are provided for signals with 500 ps and 1000 ps rise times.

The following sections describe the recommended termination network

and how to select components for a target system.

- "Designing a Discrete RCR Termination Network" on page 47

- "Equivalent Load" on page 48

- "Extrapolating T1 and T2 Trace Lengths" on page 49

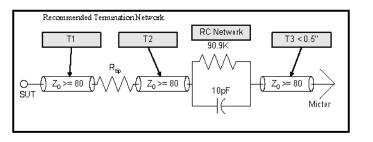

**Designing a Discrete RCR Termination Network.** Refer to the following schematic diagram for designing a discrete termination network.

| SUT<br>Risetime | T1 Length  | T2 Length  | T3 Length  | T1/T2/T3<br>Impedance | Rtip     |

|-----------------|------------|------------|------------|-----------------------|----------|

| >= 1ns          | <= 1.4 in. | <= 1.4 in. | <= 0.5 in. | Z0 >= 80 ohms         | 196 ohms |

| >= 500ps        | <= 0.7 in. | <= 0.7 in. | <= 0.5 in. | Z0 >= 80 ohms         | 215 ohms |

The key parameter to consider when designing a discrete probing network is the rise time of the signal under test. Maximum trace lengths and tip resistor values are dependent upon the rise time.

NOTE:

The previous values are derived from complex equations that are a function of the logic analyzer connector and cabling electrical characteristics, input network, standard component values, trace impedance and length, and parasitic capacitance and inductance . It is beyond the scope of this document to provide these equations for general discussion. If the maximum trace lengths specified here are not sufficient to probe the signal under test, please consult an Agilent Technologies technical specialist.

T1, T2, and T3 are all 80 ohms or higher printed-circuit board traces on the target system that connect the various components in the probing network. It is important to keep the trace impedance as high as possible. It is recommended that outer layers be used which minimize the capacitance and maximize the impedance and propagation speeds. In general, design the trace on an outer layer with as high impedance

# Chapter 4: Concepts Passively Probing an InfiniBand System

as possible without implementing out of the ordinary design techniques such as ground plane cutouts. Keep the trace lengths within the tolerances specified in the table.

The tip resistor Rtip must be placed within T1length of the signal under test (SUT). The trace length and tip resistor have been selected to provide maximum frequency response into the logic analyzer input network.

The RC network is connected to Rtip via a printed-circuit trace T2 which should not exceed T2length. Use precision 0402 or 0603 surface mount components for this network (1% R, 5% C).

The Mictor connector should be placed as close to the RC network as possible, not to exceed T3length = 0.5 inches in printed-circuit board trace length. The input impedance of the connector and logic analyzer cable is 120 ohms. In practice it is very difficult to achieve a matched impedance printed-circuit board trace, resulting in an inevitable mismatch. To keep the reflections from degrading the setup and hold margins, the maximum length of T3 has been specified in the previous table.

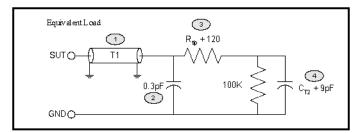

**Equivalent Load.** The discrete probing network and the logic analyzer input can be modeled as the following equivalent load.

- 1. T1 is a printed-circuit board trace transmission line specified in Section 2.2.1. Rtip is the sum of the tip resistor and the logic analyzer cable impedance.

- 2. The 0.3pF capacitance is the parasitic capacitance of the tip resistor pads.

- 3. The equivalent series resistance is the sum of the tip resistor Rtip and the 120 ohm (DC component) logic analyzer cable impedance.

4. The capacitive load is the sum of the logic analyzer capacitance plus the T2 printed-circuit board transmission line lumped capacitance. Assuming T2 has a length of 1.4 inches and a 2pF per inch capacitance, the equivalent capacitive load can be calculated by the following equation:

```

Cequiv = 9pF + T2pF/in * T2length = 9pF + 2pF/in * 1.4 in. = 11.8pF

```

**Extrapolating T1 and T2 Trace Lengths.** It is fairly straightforward to extrapolate the previous values for faster, slower, and intermediate rise times. For signals with rise times faster than 300 ps, a more detailed analysis must be performed. Refer to the following equations for calculating the optimal maximum trace length for the T1 and T2 printed-circuit board traces. Note that the following lengths are only approximations since the resistor values are selected to be compatible with industry standard components.

## **Routing Techniques**

Regardless of whether discrete networks are used or not, the following describes some general guidelines for probing high-speed signals and buses. Low voltage TTL logic (LVTTL) and SSTL logic buses are described here.

**NOTE:** The following schematics are meant to be a basic guide for probing placement, not a description of how to terminate transmission lines. Please refer to the vendors documentation for exact termination techniques.

- "Series Terminated LVTTL" on page 49

- "Load Terminated LVTTL" on page 50

- "SSTL-2" on page 50

- "SSTL-3" on page 50

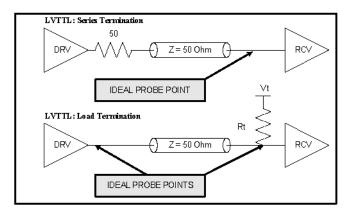

**Series Terminated LVTTL.** Series termination resistors can be used to dampen reflections on traces exceeding the length equals 1/5 rise time rule. Signals propagating along a source series transmission line resolve at the load. Midpoints along the transmission line will contain a partial signal rise until the reflection returns and completes the

transition. If the intermediate step function voltage happens to be near the threshold voltage of the logic analyzer, metastability may occur and ultimately degrade setup and hold margins into the logic analyzer. Series terminated transmission lines should be probed at the load.

**Load Terminated LVTTL.** Uni-directional and bi-directional load terminated transmission lines can generally be probed at the driver, load, or anywhere in between as long as all signals are probed at the same position. It is important to keep the stub lengths less than 1/5 the rise time. Ideally, one endpoint should be selected for probing.

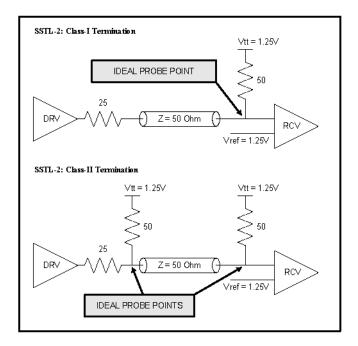

**SSTL-2.** The Agilent SerDes drives/receives signals in an SSTL-2 format. While SSTL-2 provides excellent high-speed signal fidelity during transmission across a printed-circuit board, issues arise that do not normally occur with single-ended LVTTL logic.

An SSTL-2 transmission line is described by the following diagram. Class-I termination specifies a 50 ohm resistor to Vtt at the receiver. Class-II termination requires a 50 ohm resistor to Vtt at both the source and receiver. A 25 ohm series resistor is typically designed into the driver. In general, it is safe to probe the signal at or very near the load termination resistors, which may be either end for Class-II buses.

**SSTL-3.** The technique for termination and probing 3.3V SSTL logic is the same except the bias voltage is higher and the logic analyzer threshold must be set to 1.5V instead of 1.25V.

# Logic Analyzer Connectors

- "Mictor Connectors" on page 51

- "Connector Placement Techniques" on page 51

- "Mictor Connector Pinout" on page 52

## **Mictor Connectors**

Mictor Connectors are used to connect the signal under test (SUT) to the logic analyzer. The connectors each provide for 32 signals plus two clocks. The Mictor connectors each have 38 surface mount pins plus 5 through-hole ground returns. Mechanical documentation and layout information can be found on the Agilent Technologies web site.

## **Connector Placement Techniques**